Le MCP23017 de Microchip est une extension d’entrées / sorties (GPIO) 16 bits sur bus I2C. Il existe des variantes qui combinent 8 ou 16 bits, sur ports I2C ou SPI.

Description

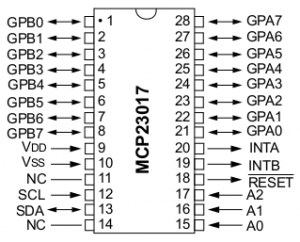

Le schéma ci-contre donne le brochage d’un MCP23017. Le MCP23S17 est le même, mais avec un port SPI en lieu et place du port I2C. 4 broches diffèrent sur le MCP23S17 :

- Broche 11: CS

- Broche 12: SCK

- Broche 13: SI

- Broche 14: SO

Les broches 15 à 17 définissent l’adresse du MCP23017, ce qui permet d’en relier jusqu’à 8 sur un même bus I2C, pour un maximum de 128 broches d’entrées / sorties par bus I2C.

L’alimentation (Vdd) est comprise entre 1,8 v et 5,5 v. Ce qui le rend compatible avec les micro-contrôleurs et micro-processeurs 3,3 v et 5 v.

Les 16 entrées / sorties sont utilisables individuellement ou par ports de 8 bits.

Chacun des deux ports dispose d’une sortie d’interruption (INTA et INTB) qui permet d’en propager le déclenchement sur le système hôte.

La famille du MCP23017 est constituée de plusieurs membres :

| Modèle | Nb de bits | Interface | Vitesse bus |

|---|---|---|---|

| MCP23008 | 8 | I2C | 1,7 Mbps |

| MCP23009 | 8 | I2C | 3,4 Mbps |

| MCP23017 | 16 | I2C | 1,7 Mbps |

| MCP23018 | 16 | I2C | 3,4 Mbps |

| MCP23S08 | 8 | SPI | 10 Mbps |

| MCP23S09 | 8 | SPI | 10 Mbps |

| MCP23S17 | 16 | SPI | 10 Mbps |

| MCP23S18 | 16 | SPI | 10 Mbps |

Note: Le MCP23016 est déprécié par le fabricant.

Utilisation

Configuration de l’adresse

L’adresse du MCP23017 est constituée de 4 bits imposés (0100), 3 bits utilisateur (voir tableau suivant), et un bit de lecture / écriture (0 en écriture et 1 en lecture). La gestion du bit de lecture / écriture se fait au niveau du protocole série, et doit généralement être ignoré par l’application utilisatrice. L’adresse peut donc varier de 0x20 à 0x27 (ou de 0x40 à 0x4F si vous devez gérer vous-même le bit d’écriture), ce qui permet d’adresser jusqu’à 8 MCP23017 sur un port I2C.

Les trois bits d’adresse utilisateur correspondent aux broches 15 à 17 d’un MCP23017, qui doivent êtres toutes connectées. Dans le tableau suivant, ceux indiqués à 1 sont reliés à l’alimentation (Vdd), et ceux indiqués à 0 sont reliés à la masse (Vss).

| A2 | A1 | A0 | Adresse |

|---|---|---|---|

| 0 | 0 | 0 | 0x20 |

| 0 | 0 | 1 | 0x21 |

| 0 | 1 | 0 | 0x22 |

| 0 | 1 | 1 | 0x23 |

| 1 | 0 | 0 | 0x24 |

| 1 | 0 | 1 | 0x25 |

| 1 | 1 | 0 | 0x26 |

| 1 | 1 | 1 | 0x27 |

Référence des registres

Chaque commande envoyée au MCP23017 prend la forme d’une adresse de registre suivie de 8 bits de paramètres. Chaque registre est doublé. Un exemplaire commande le port GPIO A (sur fond blanc, et l’autre commande le port GPIO B (sur fond bleu).

Le tableau suivant correspond à la configuration par défaut, où le paramètre BANK du registre IOCON vaut 0. Vous trouverez la version de ce tableau en configuration IOCON/BANK = 1 pages 9 à 11 de la datasheet.

| Registre | Adresse | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Déf |

|---|---|---|---|---|---|---|---|---|---|---|

| IODIRA | 0x00 | IO7 | IO6 | IO5 | IO4 | IO3 | IO2 | IO1 | IO0 | 0xFF |

| IODIRB | 0x01 | IO7 | IO6 | IO5 | IO4 | IO3 | IO2 | IO1 | IO0 | 0xFF |

| IPOLA | 0x02 | IP7 | IP6 | IP5 | IP4 | IP3 | IP2 | IP1 | IP0 | 0x00 |

| IPOLB | 0x03 | IP7 | IP6 | IP5 | IP4 | IP3 | IP2 | IP1 | IP0 | 0x00 |

| GPINTENA | 0x04 | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0x00 |

| GPINTENB | 0x05 | GPINT7 | GPINT6 | GPINT5 | GPINT4 | GPINT3 | GPINT2 | GPINT1 | GPINT0 | 0x00 |

| DEFVALA | 0x06 | DEF7 | DEF6 | DEF5 | DEF4 | DEF3 | DEF2 | DEF1 | DEF0 | 0x00 |

| DEFVALB | 0x07 | DEF7 | DEF6 | DEF5 | DEF4 | DEF3 | DEF2 | DEF1 | DEF0 | 0x00 |

| INTCONA | 0x08 | IOC7 | IOC6 | IOC5 | IOC4 | IOC3 | IOC2 | IOC1 | IOC0 | 0x00 |

| INTCONB | 0x09 | IOC7 | IOC6 | IOC5 | IOC4 | IOC3 | IOC2 | IOC1 | IOC0 | 0x00 |

| IOCON | 0x0A | BANK | MIRROR | SEQOP | DISSLW | HAEN | ODR | INTPOL | — | 0x00 |

| IOCON | 0x0B | BANK | MIRROR | SEQOP | DISSLW | HAEN | ODR | INTPOL | — | 0x00 |

| GPPUA | 0x0C | PU7 | PU6 | PU5 | PU4 | PU3 | PU2 | PU1 | PU0 | 0x00 |

| GPPUB | 0x0D | PU7 | PU6 | PU5 | PU4 | PU3 | PU2 | PU1 | PU0 | 0x00 |

| INTFA | 0x0E | INT7 | INT6 | INT5 | INT4 | INT3 | INT2 | INT1 | INT0 | 0x00 |

| INTFB | 0x0F | INT7 | INT6 | INT5 | INT4 | INT3 | INT2 | INT1 | INT0 | 0x00 |

| INTCAPA | 0x10 | ICP7 | ICP6 | ICP5 | ICP4 | ICP3 | ICP2 | ICP1 | ICP0 | 0x00 |

| INTCAPB | 0x11 | ICP7 | ICP6 | ICP5 | ICP4 | ICP3 | ICP2 | ICP1 | ICP0 | 0x00 |

| GPIOA | 0x12 | GP7 | GP6 | GP5 | GP4 | GP3 | GP2 | GP1 | GP0 | 0x00 |

| GPIOB | 0x13 | GP7 | GP6 | GP5 | GP4 | GP3 | GP2 | GP1 | GP0 | 0x00 |

| OLATA | 0x14 | OL7 | OL6 | OL5 | OL4 | OL3 | OL2 | OL1 | OL0 | 0x00 |

| OLATB | 0x15 | OL7 | OL6 | OL5 | OL4 | OL3 | OL2 | OL1 | OL0 | 0x00 |

IODIRp : Registre de direction. Contrôle la direction des entrées / sorties du port GPIO p. Quand un bit (IOb) est à 1, la broche correspondante (b) du GPIO p est en entrée. Quand un bit (IOb) est à 0, la broche correspondante (b) du GPIO p est en sortie. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 1 au démarrage (0xFF).

IPOLp : Registre de polarité en entrée. Contrôle la polarité des entrées du port GPIO p. Quand un bit (IPb) est à 1, le registre correspondant (b) reflétera l’inverse de l’état logique appliqué à la broche b du GPIO p. Quand un bit (IPb) est à 0, le registre correspondant (b) reflétera l’état logique appliqué à la broche b du GPIO p. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

GPINTENp : Registre d’interruption sur changement. Contrôle la fonction d’interruption sur changement de chaque broche du port GPIO p. Quand un bit (GPINTb) est à 1, l’interruption sur changement est activée pour la broche correspondante (b) du GPIO p. Les registres DEFVALp et INTCONp doivent aussi être paramétrés, dans ce cas. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

DEFVALp : Registre de valeur initiale du comparateur d’interruption sur changement. S’il est activé (via GPINTENp et INTCONp), la présence d’un état logique inverse à celui fourni sur la broche correspondante du GPIO déclenchera une interruption sur changement. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

INTCONp : Registre de contrôle d’interruption. Contrôle le comparateur d’interruption sur changement. Quand un bit (IOCb) est à 1, l’état logique de la broche correspondante (b) du GPIO p est comparée au bit associé du registre DEFVALp. Quand un bit (IOCb) est à 0, l’état logique de la broche correspondante (b) du GPIO p est comparée à sa valeur précédente. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

IOCON : Registre de configuration. Contrôle la configuration du MCP23017 :

BANK : Ce bit change la table d’adressage du registre de commandes. Lorsque le bit BANK est mis à 1, les registres sont groupés par port GPIO. Les registres du port A sont dans la plage d’adresses 0x00 à 0x0A et les registres du port B sont dans la plage d’adresses 0x10 à 0x1A. Lorsque le bit BANK est mis à 0, les registres sont groupés par fonctionnalité. Par exemple, IODIRA sera à l’adresse 0x00 et IODIRB à l’adresse suivante (0x01). Gardez bien à l’esprit que mettre à jour ce bit va modifier toute la table des registres, et il faut éviter de le modifier lors de traitements par lots.

MIRROR : Ce bit contrôle la façon dont les broches INTA et INTB fonctionnent l’une par rapport à l’autre. Quand MIRROR vaut 1, un OU logique sera appliqué sur les deux broches. Le déclenchement d’une interruption sur l’un des ports GPIO sera répercuté sur les deux broches INTp. Quand MIRROR vaut 0, chaque broche d’interruption est indépendante. Une interruption sur le GPIOp ne sera répercutée que sur INTp.

SEQOP : Bit d’opérations séquentielles. Ce bit contrôle l’auto-incrément du pointeur d’adresse. Quand SEQOP vaut 1, l’auto-incrément du pointeur d’adresse est désactivé. Quand SEQOP vaut 0, le pointeur d’adresse s’incrémente a chaque octet envoyé à travers le port série.

DISSLW : NDT: Ce paramètre n’est pas clair à mes yeux et je préfère ne pas le traduire. Voir la page 17 de la datasheet pour plus d’informations.

HAEN : Gestion d’adresse matérielle. Ce bit contrôle si les 3 broches d’adresse matérielle sont utilisées. Ne fonctionne que sur un MCP23S17. Dans tous les cas, les broches correspondantes doivent êtres reliées. Lorsque HAEN vaut 1, Les 3 broches d’adresse A0 à A2 participent à l’adresse du MCP23S17. Lorsque HAEN vaut 0, les 3 broches d’adresse A0 à A2 seront ignorées et vaudront 0.

ODR : Contrôle de collecteur ouvert. Quand ODR vaut 1, les broches INTp sont à collecteur ouvert, la valeur de INTPOL sera ignorée. Quand ODR vaut 0, les broches INTp disposeront d’une résistance de rappel ou de tirage interne, selon la valeur de INTPOL.

INTPOL : Contrôle de polarité d’interruption. Quand INTPOL vaut 1, les broches INTp disposeront d’une résistance de tirage (pull-up) interne. Quand INTPOL vaut 0, les broches INTp disposeront d’une résistance de rappel (pull-down) interne.

Le bit 0 du registre IOCON n’est pas utilisé et apparaîtra toujours comme valant 0. Les autres bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

GPPUp : Registre de contrôle des résistances de tirage (pull-up). Quand un bit (PUb) est à 1, la broche correspondante (b) du GPIO p dispose d’une résistance de tirage (pull-up) interne de 100 kΩ. Quand un bit (PUb) est à 0, la broche correspondante (b) du GPIO p ne dispose pas d’une résistance de tirage (pull-up) interne. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

INTFp : Registre des interruptions. Ce registre reflète les interruptions de chaque broche pour lesquelles elles ont été activées par le registre GPINTEN. Un bit (INTb) à 1 signifie que la broche (b) correspondante du port GPIO p a déclenché une interruption. Un bit (INTb) à 0 signifie que la broche (b) correspondante du port GPIO p n’a pas déclenché d’interruption (ou n’est pas paramétrée pour en déclencher). Tous les bits sont accessibles en lecture seule. Toute écriture sera ignorée. Tous les bits sont à 0 au démarrage (0x00).

INTCAPp : Registre de capture des interruptions. Ce registre en lecture seule capture l’état du port GPIO p au déclenchement d’une interruption. Il conserve son état jusqu’à la lecture de INTCAP ou de GPIO. Tous les bits sont accessibles en lecture seule. Son état au démarrage est inconnu.

GPIOp : Le registre GPIOp reflète les états logiques du port GPIO p. Toute écriture dans ce registre est appliquée au registre OLATp. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

OLATp : Le registre OLATp donne accès aux bascules de sortie. Une lecture reflétera l’état des bascules, et non le port lui-même. Une écriture dans ce registre modifiera les bascules, qui à leur tour modifieront les broches configurées en sortie. Tous les bits sont accessibles en lecture et écriture. Tous les bits sont à 0 au démarrage (0x00).

Applications

Voici quelques exemples d’application du MCP23017 :

- Création ou extension de ports GPIO

- Pilotage de composants parallèle (afficheur à LEDs, LCD, etc)

- Pilotage de relais

- Gestion de claviers matriciels

- Gestion de capteurs binaires (ILS / REED, PIR, niveau de liquide, etc)

Liens

- Voir la datasheet

- Microchip.com : Le MCP23017

bonjour

avez vous un fichier d exemple a me fournir pour les interruptions

Bonjour, j’ai commencé à rédiger un second article sur la mise en œuvre du MCP23017 avec un RaspberryPi. Mais j’ai énormément de travail ces derniers temps, et l’ai un peu mis de côté. Je ne me suis pas encore trop penché sur la gestion des interruptions, mais puisque le sujet intéresse du monde, je vous promets de le faire !

Bonjour,

Felecitation pour votre site.

J’essaye de mettre en oeuvre plusieurs mcp23017 sur le meme bus. De facon a avoir 32 entrees et 32 sorties.

Ils sont raccordé a un raspberry pi.

Les sorties sont gérées parfaitement, les entrees j’ai un peu plus de mal surtout pour gerer les interruptions.

Je n’ai pas bien compris a quoi sert le registre DEFVALp ainsi que le registre INTCONp.

Pourriez vous m’expliquer?

Merci

jc

Bonjour, je n’ai pas encore travaillé sur la gestion d’interruptions de ce composant. Je vais donc répondre très théoriquement. Le registre INTCON contrôle le mode de comparaison du gestionnaire d’interruption. Un bit à 0 signifie qu’une interruption devra être levée lorsque la broche correspondante du GPIO changera d’état. Il se compare à lui même. Une valeur de 1 signifie qu’une interruption devra être levée lorsque la broche correspondante du GPIO aura un état différent de ce qui est indiqué dans le registre DEFVAL. Il se compare à DEFVAL. Les interruptions sont gérées par un registre comparateur dont la valeur initiale est paramétrée par le registre DEFVAL.

Par exemple, si le premier bit vaut 0 dans INTCON, une interruption devra être levée à chaque changement d’état (aussi bien 0 que 1). Le registre DEFVAL est ignoré pour ce bit. Si le bit vaut 1 dans INTCON et 0 dans DEFVAL, seuls les passages de 0 à 1 doivent déclencher une interruption. Le retour à 0 ne doit pas en déclencher.